[ Instrument Network Instrument R & D ] As an important application field of the emerging information industry, the trillion-level market of the Internet of Things is gradually forming. Super-trillion-level devices and nodes will realize the interconnection of everything and the intelligent connection of everything through the Internet of Things technology. Limited by factors such as volume, weight, and cost, IoT nodes (such as wearable devices, smart home nodes, wireless sensor nodes, environmental monitoring nodes, etc.) need to be able to work continuously under the condition of power supplied by micro batteries or energy harvesting technologies For years or even more than a decade, this has imposed harsh low-power requirements on the chip.

More advanced integrated circuits are the "core" of microprocessors or multi-core processors, which can control everything from computers to mobile phones to digital microwave ovens. Memory and ASICs are examples of other integrated circuit families and are very important for the modern information society. Although the cost of designing and developing a complex integrated circuit is very high, the cost per IC is minimized when it is spread across the usually millions of products. The performance of the IC is very high, because the small size brings short paths, allowing low-power logic circuits to be used at fast switching speeds.

At present, the main research direction of reducing the power consumption of IoT chips is based on a dedicated wake-up chip based on the periodic operating mode (for example, a dedicated voice recognition wake-up chip). By placing the chip in a periodic "sleep-wake" switching state, To achieve the purpose of reducing power consumption; however, IoT nodes usually work in the "random sparse event" scenario. In order to avoid losing events that may occur at any time, the frequency of "sleep-wake" is usually much higher than the true incidence of events. This leads to serious waste of power.

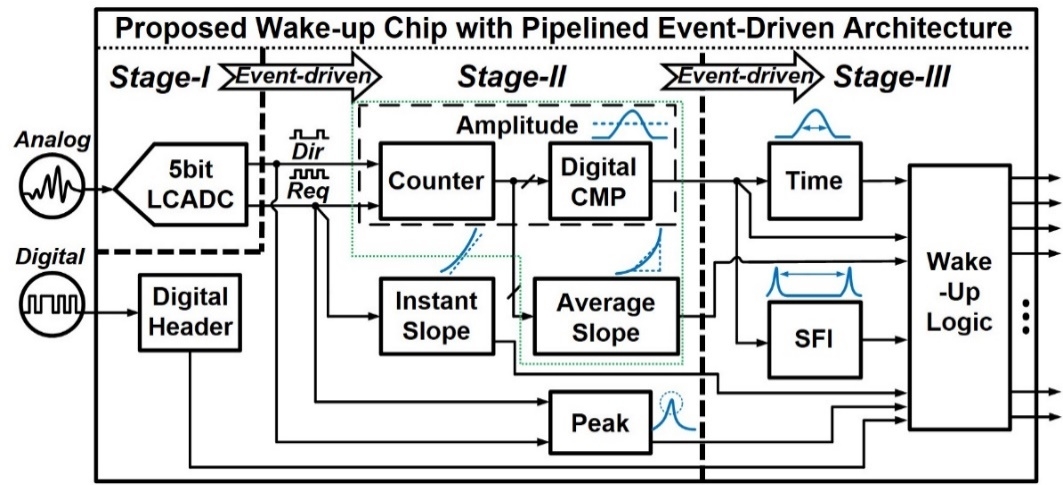

Academician Huang Ru-Associate Professor Ye Le from the Department of Micro-Nano Electronics, Peking University School of Information Science and Technology, cooperated with the Peking University Advanced Institute of Information Technology, Shanghai Core Wing Information Technology Co., Ltd., and proposed multi-level asynchronous flow for the first time in the world. The event-driven chip architecture transforms the traditional periodic working mode into an asynchronous event-driven working mode, which significantly reduces the power consumption of IoT nodes in the "random sparse event" scenario.

In addition, the research group also proposed the time-domain shielded threshold-crossing analog-to-digital converter Level-CrossingADC (LC-ADC) technology, which solves the problem inherent in traditional LC-ADCs: “noise false triggering leads to functional errors and increased power consumptionâ€. Difficulties; and the design of a multi-function signal feature judger circuit based on time-domain pulse signal processing technology, which implements a combination of signal features such as amplitude, slope, time interval, wave crest, trough, etc. through offline or online software-defined methods to meet In addition, the chip has no clock signal and clock network, eliminating the main source of power consumption of the chip in the standby state.

Based on the above-mentioned innovative technologies, the research team developed a very low-power IoT universal wake-up chip with an average power consumption of only 57 nanowatts, which is 30 times higher than the current best level of similar international work. This chip demonstrates typical IoT application scenarios such as heart rate abnormality warning, ECG T-wave abnormality warning, epilepsy warning, voice keyword envelope wake-up, etc. The chip cooperates with high-performance modules such as microcontroller MCU chips to ensure extremely low power. To achieve more complex wake-up functions of the Internet of Things under the premise of power consumption. The asynchronous pipeline event-driven architecture proposed for the first time in this work provides a research idea and a solution path to break through the existing power bottlenecks for the research of the ultra-low-power IoT chip field.

Blank type forklift forks, We can make any size you want, the material is 42 Crmo, thicker heel, our forks' capacity range from 0.5ton to 80ton. Quality assurance for one year, we have passed the ISO9000 and CE certification, please feel free to purchase.

Blank Type Forks,Blank Fork Arms,Blank Forklift Forks,Blank Type Pallet Fork

Shandong Techence Forging Co.,Ltd , https://www.shandongtechence.com